近日,中国科大微电子学院胡诣哲与林福江课题组设计的一款基于全新电荷舵采样(Charge-SteeringSampling, CSS)技术的极低抖动毫米波全数字锁相环(CSS-ADPLL)芯片入选2023 Symposium on VLSI Technology and Circuits(以下简称VLSI Symposium)。VLSI Symposium是超大规模集成电路芯片设计和工艺器件领域最著名的国际会议之一,也是展现IC技术最新成果的橱窗,今年VLSI Symposium于6月11日至16日在日本京都举行。该论文第一作者为我校微电子学院博士生陶韦臣,胡诣哲教授为通讯作者。

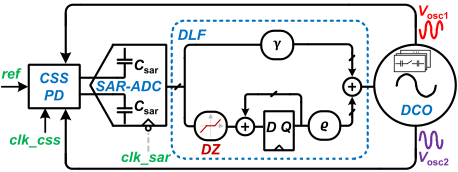

极低抖动毫米波频率综合器芯片是实现5G/6G毫米波通信的关键核心模块,为毫米波通信提供精准的载波信号。此研究提出的电荷舵采样技术,将电荷舵采样和逐次逼近寄存器型模数转换器(SAR-ADC)进行了巧妙的结合,构建了一种高鉴相增益,高线性度且具有多bit数字输出的数字鉴相器。CSS-ADPLL的结构十分紧凑(如图1所示),由电荷舵鉴相器(CSS-PD)、SAR-ADC、数字滤波器和数控振荡器组成,具有优异相位噪声性能,较快的锁定速度并消耗极低的功耗。

图1.论文提出的电荷舵采样全数字锁相环(CSS-ADPLL)架构

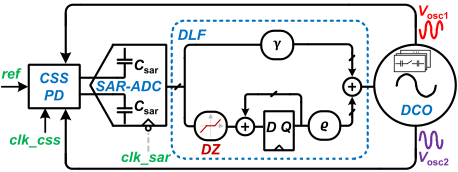

测试结果表明,该芯片实现了75.9fs的时钟抖动与–50.13dBc的参考杂散,并取得了-252.4dB的FoM值,为20GHz以上数字锁相环的最佳水平,芯片核心面积仅为0.044mm2。该研究成果以“An 18.8-to-23.3 GHz ADPLL Based on Charge-Steering-Sampling Technique Achieving 75.9 fs RMS Jitter and -252 dB FoM”为题由博士生陶韦辰在大会作报告。

图2.CSS-ADPLL相位噪声与参考杂散测试结果

图3.第一作者陶韦臣博士在大会作报告

图4.部分论文作者合照:胡诣哲教授(右一)与Staszewski教授(右三)

该研究工作得到了科技部国家重点研发计划资助,也得到了中国科大微电子学院、中国科大信息科学技术学院支持。

大会官网:[backcolor=transparent !important]https://www.vlsisymposium.org

(微电子学院、科研部)

| 欢迎光临 中科大家长论坛 (http://ustcjz.com/) | Powered by Discuz! X3.4 |